Projekat: ENA signal...

Pozdrav svima!

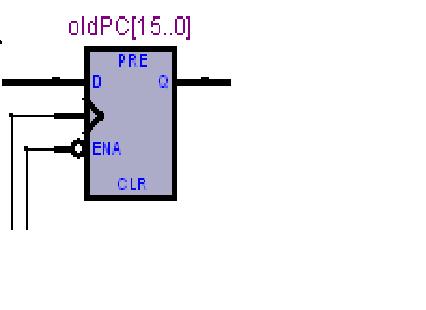

U attachmentu ove poruke je slika flip-flopa/registra na RTL nivou koju je

nacrtao Quartus-ov "RTL viewer". Ovo predstavlja osnovnu memorijsku jedinicu

(ili grupu tih jedinica) na FPGA čipu a ne neki moj entitet. Ako ne se ne

vidi slika, bitno je da jedinica ima ulazne signale D, clk i clr i izlazni

signal Q sa uobičajenim značenjem i još jedan ulazni signal - ENA.

Zanima me da li neaktivna vrednost signala ENA samo onemogućava upisivanje

novog stanja u jedinicu ili takođe onemogućava i čitanje stanja?

Dizajn radim, kao što sam već napisao, u Quartus-u, a za sintezu koristim

Cyclone II familiju uređaja.

Hvala unapred.

U attachmentu ove poruke je slika flip-flopa/registra na RTL nivou koju je

nacrtao Quartus-ov "RTL viewer". Ovo predstavlja osnovnu memorijsku jedinicu

(ili grupu tih jedinica) na FPGA čipu a ne neki moj entitet. Ako ne se ne

vidi slika, bitno je da jedinica ima ulazne signale D, clk i clr i izlazni

signal Q sa uobičajenim značenjem i još jedan ulazni signal - ENA.

Zanima me da li neaktivna vrednost signala ENA samo onemogućava upisivanje

novog stanja u jedinicu ili takođe onemogućava i čitanje stanja?

Dizajn radim, kao što sam već napisao, u Quartus-u, a za sintezu koristim

Cyclone II familiju uređaja.

Hvala unapred.

- Follow-Ups:

- Re: Projekat: ENA signal...

- From: Sasa Stojanovic <stojsasa@yahoo.com>

- Re: Projekat: ENA signal...

Previous by date: Re: Pitanje u vezi projekta

Next by date: Re: Projekat: ENA signal...

Previous by thread: Re: Pitanje u vezi projekta Next by thread: Re: Projekat: ENA signal...

Previous by thread: Re: Pitanje u vezi projekta Next by thread: Re: Projekat: ENA signal...